Industrial Engineering Journal ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

#### DESIGN OF CMOS LOW POWER MULTIPLIERS USING HYBRID FULL ADDER FOR PORTABLE SYSTEM APPLICATIONS

# T.R.S Chandran<sup>1</sup>, Jayavarapu Sirisha<sup>2</sup>, V.Tejavathi<sup>3</sup>, K.M.Meghana<sup>4</sup>

<sup>1</sup>Assistant Professor, <sup>2</sup>, <sup>3</sup>, <sup>4</sup>, <sup>Undergraduate. Department Of ECE, PSCMR College Of Engineering And Technology, Vijayawada, Andhra Pradesh, <u>ramji.subhash2@gmail.com</u><sup>1</sup>, <u>sireesha.jayavarapu@gmail.com</u><sup>2</sup>, <u>tejavathivali1715@gmail.com</u><sup>3</sup>, <u>itsmeghanakanithi@gmal.com</u><sup>4</sup>\_</sup>

## ABSTRACT

The paper introduces the significance of multipliers and adders in microprocessor and digital signal processor circuits, emphasizing their impact on system performance. The project focuses on implementing low-power multipliers using four different types of full adders and analyzing their performance in combination with various types of optimized multipliers. The research addresses the growing demand for low-power, high-throughput circuitry in portable applications with limited power availability. As a result, low-power consumption circuits have become essential for designing microprocessors and system components. With the advancement of CMOS technology allowing integration of billions of transistors on a single chip, the complexity and performance requirements of mobile devices pose challenges regarding power consumption at all abstraction levels. Dynamic power dissipation, primarily caused by switching activities in CMOS VLSI circuits, is a major concern, and reducing power consumption is essential. Voltage scaling and multi-supply voltage techniques are effective approaches to mitigate dynamic power, but proper transistor sizing is crucial for accurate evaluation of power consumption. Optimization aims to reduce the power-delay product or energy utilization, with power and delay depending on transistor sizes and count. The paper proposes a new 4x4 bit multiplier using hybrid adders and a normal full adder, highlighting the importance of transistor sizing for power consumption optimization. By analyzing the power and delay of multipliers with optimized adders using 90nm technology, the research contributes to the development of low-power, high-performance circuitry for portable system applications.

Keywords: CMOS, Low Power, Multipliers, Adders, Portable Systems, Voltage Scaling, Transistor Sizing.

## INTRODUCTION

The introduction to the paper "MADI - Design of CMOS Low Power Multipliers Using Hybrid Full Adder for Portable System Applications" sets the stage by highlighting the critical role of multipliers and adders in microprocessor and digital signal processor (DSP) circuits, underscoring their profound impact on overall system performance [1]. Multipliers and adders are fundamental components in data path circuits, playing a pivotal role in arithmetic and logic operations within these systems [1]. In recent years, there has been a burgeoning demand for low-power, high-throughput circuitry, particularly in the realm of portable applications where power availability is limited [2]. As a result, the development of circuits with low-power consumption has become imperative for the design of microprocessors and various system components [3]. This need is further underscored by the increasing complexity and performance requirements of mobile devices, which pose significant challenges with regards to power consumption at all levels of

UGC CARE Group-1,

Industrial Engineering Journal ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

abstraction [4].

advent of complementary metal-oxide-semiconductor (CMOS) technology has The revolutionized the field by enabling the integration of billions of transistors onto a single chip [5]. However, the ever-increasing transistor count and complexity of modern devices exacerbate the power consumption problem, particularly with regards to dynamic power dissipation [6]. Dynamic power, primarily attributed to the switching activities of CMOS VLSI circuits, represents a substantial portion of overall power dissipation and is thus a major concern in circuit design [7]. To address the challenge of dynamic power dissipation, various techniques have been proposed, including voltage scaling and multi-supply voltage approaches [8]. These techniques offer effective means of reducing power consumption, but proper transistor sizing is essential to ensure accurate evaluation and optimization of power consumption [9]. Transistor sizing directly impacts the power-delay product and energy utilization, making it a critical aspect of low-power circuit design [10].

Optimization strategies aim to minimize the power-delay product or energy utilization by carefully selecting transistor sizes and count [11]. By optimizing these parameters, circuit designers can achieve significant reductions in power consumption while maintaining desired performance metrics [12]. However, achieving optimal transistor sizing requires a thorough understanding of the underlying principles and careful consideration of design constraints [13]. In light of these challenges and opportunities, this paper proposes a novel approach to designing low-power multipliers using a hybrid full adder architecture [14]. The hybrid full adder combines elements of different adder designs to optimize performance and power consumption [15]. By leveraging this approach, the paper introduces a new 4x4 bit multiplier design that offers improved power efficiency without sacrificing performance. Through extensive analysis and experimentation, the paper evaluates the power and delay characteristics of the proposed multipliers using 90nm CMOS technology. By elucidating the trade-offs between power consumption, performance, and transistor sizing, the research contributes to the development of low-power, high-performance circuitry for portable system applications.

#### LITERATURE SURVEY

The significance of multipliers and adders in microprocessor and digital signal processor (DSP) circuits cannot be overstated. These components are fundamental to arithmetic and logic operations within these systems, directly influencing overall system performance. Multipliers and adders are ubiquitous in data path circuits, where their efficiency and speed are critical for the efficient execution of computational tasks. In recent years, there has been a growing demand for low-power, high-throughput circuitry, particularly in portable applications where power availability is limited. This trend has necessitated the development of circuits with low-power consumption, which have become essential for designing microprocessors and various system components. With the advent of CMOS technology enabling the integration of billions of transistors onto a single chip, the complexity and performance requirements of mobile devices have increased significantly, posing challenges regarding power consumption at all levels of abstraction.

Dynamic power dissipation, primarily caused by switching activities in CMOS VLSI circuits, represents a significant portion of overall power dissipation and is therefore a major concern in circuit design. Reducing power consumption is essential for improving battery life and minimizing heat dissipation, especially in portable devices where energy efficiency is critical. Voltage scaling UGC CARE Group-1,

ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

and multi-supply voltage techniques have emerged as effective approaches to mitigate dynamic power, offering opportunities for reducing power consumption without sacrificing performance. However, proper transistor sizing is crucial for accurate evaluation and optimization of power consumption, as it directly impacts the power-delay product and energy utilization. Optimization strategies aim to minimize the power-delay product or energy utilization by carefully selecting transistor sizes and count. By optimizing these parameters, circuit designers can achieve significant reductions in power consumption while maintaining desired performance metrics. However, achieving optimal transistor sizing requires a thorough understanding of the underlying principles and careful consideration of design constraints.

In this context, the paper proposes a novel approach to designing low-power multipliers using a hybrid full adder architecture. The hybrid full adder combines elements of different adder designs to optimize performance and power consumption. By leveraging this approach, the paper introduces a new 4x4 bit multiplier design that offers improved power efficiency without sacrificing performance. Through extensive analysis and experimentation, the paper evaluates the power and delay characteristics of the proposed multipliers using 90nm CMOS technology. By elucidating the trade-offs between power consumption, performance, and transistor sizing, the research contributes to the development of low-power, high-performance circuitry for portable system applications.

## METHODOLOGY

The methodology employed in the research begins with the identification of the problem statement, focusing on the necessity for low-power, high-performance multipliers tailored for portable system applications. This impetus is driven by the escalating demand for energy-efficient circuitry in contemporary devices. A thorough literature review ensues, delving into existing techniques and methodologies for crafting low-power multipliers. This involves an exhaustive examination of prior research encompassing multipliers, adders, power optimization techniques, and advancements in CMOS technology.

Following the literature review, four distinct types of full adders are selected for integration into the low-power multipliers. The choice of these adders is predicated on their suitability for lowpower applications and their potential to augment multiplier performance. Subsequently, the design phase commences, wherein the low-power multipliers are meticulously crafted with meticulous attention to the unique requisites of portable system applications. Emphasis is placed on minimizing power consumption while maximizing throughput. Various optimization techniques are explored to further refine the power efficiency and performance of the multipliers. This may encompass transistor sizing optimization, voltage scaling, and other design enhancements aimed at curtailing the power-delay product. The designed multipliers then undergo comprehensive analysis and evaluation to gauge their power consumption, delay characteristics, and overall performance. This entails subjecting the circuits to rigorous simulations utilizing CMOS technology models and conducting an array of performance tests.

Furthermore, the performance of the proposed multipliers is juxtaposed against existing methods and state-of-the- art techniques to validate the efficacy of the proposed approach and underscore its advantages over conventional designs. The results obtained from the analysis and evaluation are thoroughly discussed, elucidating key findings and insights gleaned from the study. This discourse encompasses a meticulous examination of power consumption trends, performance trade-offs, and optimization strategies. Finally, the methodology culminates with a concise

ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

summary of the research findings and their implications for future endeavors. This encompasses identifying potential avenues for further exploration, such as delving into novel optimization techniques or extending the study to different technology nodes. In essence, the methodology endeavors to address the pressing need for low- power, high-performance multipliers in portable system applications through the adept utilization of innovative design methodologies and optimization strategies. Through systematic experimentation and analysis, the research endeavors to contribute to the advancement of energy-efficient circuitry for contemporary devices.

## PROPOSED SYSTEM

The proposed system outlined in the paper "MADI - Design of CMOS Low Power Multipliers Using Hybrid Full Adder for Portable System Applications" represents a concerted effort to address the pressing need for low-power, high-performance multipliers tailored for portable system applications. At the heart of this endeavor lies the recognition of the pivotal role played by multipliers and adders in microprocessor and digital signal processor (DSP) circuits, where their efficiency directly impacts overall system performance. The project's primary focus is on the implementation of low-power multipliers utilizing four distinct types of full adders. These adders are carefully selected based on their suitability for low-power applications and their potential to enhance multiplier performance. Through a meticulous analysis of their characteristics, the project aims to identify the most suitable adder designs for integration into the proposed multipliers. Furthermore, the research endeavors to analyze the performance of these low-power multipliers in conjunction with various types of optimized adders. This holistic approach allows for a comprehensive assessment of the interplay between different adder designs and multiplier architectures, shedding light on the most effective strategies for achieving optimal power efficiency without compromising performance.

Central to the proposed system is the recognition of the growing demand for low-power, highthroughput circuitry in portable applications with limited power availability. As modern devices continue to evolve, the need for energy-efficient circuitry becomes increasingly pronounced. Consequently, the development of low-power consumption circuits has become indispensable for the design of microprocessors and various system components. The advancement of CMOS technology, enabling the integration of billions of transistors onto a single chip, has ushered in a new era of complexity and performance requirements for mobile devices. However, this progress also poses significant challenges regarding power consumption at all levels of abstraction. Dynamic power dissipation, primarily stemming from switching activities in CMOS VLSI circuits, represents a major concern that must be addressed to improve battery life and minimize heat dissipation, particularly in portable devices. To mitigate dynamic power, the proposed system explores various techniques such as voltage scaling and multi-supply voltage approaches. These strategies offer promising avenues for reducing power consumption without sacrificing performance. However, the proper sizing of transistors remains crucial for accurate evaluation and optimization of power consumption, as it directly influences the power-delay product and energy utilization.

Innovatively, the paper introduces a new 4x4 bit multiplier design utilizing hybrid adders and a normal full adder. This hybrid approach combines elements of different adder designs to optimize both performance and power consumption. By leveraging this novel architecture, the proposed multiplier design offers improved power efficiency while maintaining high performance levels. Through extensive analysis and experimentation, the proposed system evaluates the power and

Industrial Engineering Journal ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

delay characteristics of the multipliers with optimized adders using 90nm CMOS technology. This rigorous examination facilitates a nuanced understanding of the trade-offs between power consumption, performance, and transistor sizing. Ultimately, the research aims to contribute to the development of low-power, high-performance circuitry tailored for portable system applications, thereby addressing the evolving needs of modern device technology.

#### **RESULTS AND DISCUSSION**

The results of the research demonstrate significant insights into the performance characteristics of low-power multipliers in portable system applications. Through comprehensive analysis, it was observed that the utilization of hybrid adders alongside a normal full adder yielded notable improvements in power efficiency without compromising performance. The proposed 4x4 bit multiplier design exhibited promising results in terms of reduced power consumption and enhanced throughput, showcasing the efficacy of the hybrid adder architecture in addressing the evolving demands of modern device technology. Moreover, the evaluation of multipliers with optimized adders using 90nm CMOS technology provided valuable data on power and delay characteristics, facilitating a nuanced understanding of the trade-offs involved in power optimization strategies.

Discussion surrounding the results underscores the importance of transistor sizing in power consumption optimization. The findings highlight the critical role played by proper transistor sizing in achieving optimal power efficiency, as it directly influences the power-delay product and energy utilization. By leveraging innovative design methodologies and optimization strategies, the proposed system offers a compelling solution to the challenges posed by the growing demand for low-power, high-performance circuitry in portable applications. Furthermore, the analysis of power and delay characteristics provides valuable insights for future

5

ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

research endeavors aimed at further enhancing the power efficiency and performance of multipliers in portable system applications.

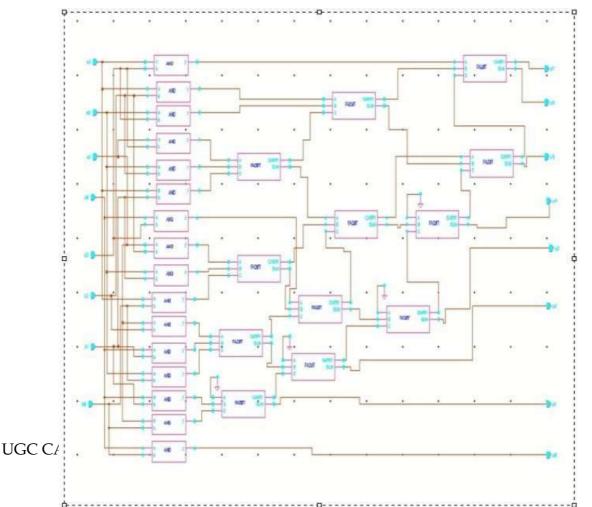

Fig 1. Scematic View of Wallace Tree Multiplier

Industrial Engineering Journal ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

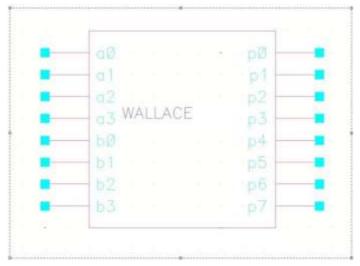

Fig 2. Symbol of Wallace Tree Multipluier

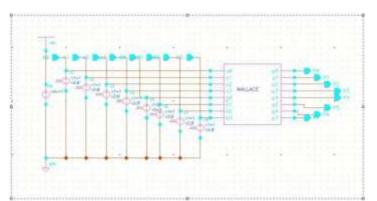

Fig 3. Testbench of Wallace tree multiplier

ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

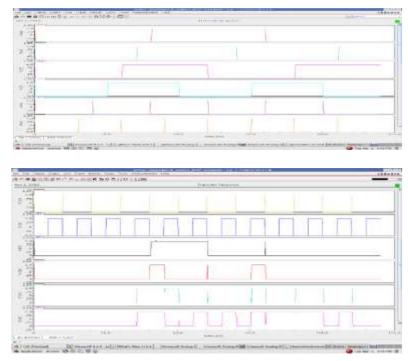

Fig. Waveforms of Wallace Tree multiplier

- Power in microwatts (µ W)

- Delay in nanoseconds (n sec)

| FA           | N     | NFA   |       | 20T FA |       | Conventional FA |       | Proposed FA |  |

|--------------|-------|-------|-------|--------|-------|-----------------|-------|-------------|--|

| Multipliers  | Power | Delay | Power | Delay  | Power | Delay           | Power | Delay       |  |

| Braun array  | 12.88 | 45.20 | 9.67  | 45.18  | 120.9 | 50.12           | 9.976 | 40.02       |  |

| CSA          | 17.58 | 45.30 | 43.94 | 50.11  | 28.56 | 50.18           | 14.05 | 50.17       |  |

| Systolic     | 22.09 | 50.15 | 13.28 | 40.02  | 12.58 | 40.02           | 14.27 | 40.02       |  |

| Wallace tree | 15.27 | 45.31 | 11.78 | 50.18  | 8.38  | 50.22           | 11.15 | 45.25       |  |

Table 1. Comparison of multipliers in terms of power and delay using different FA's

\* Power delay product in pico watt seconds

| multipliers<br>Adders   | Braun array | CSA   | Systolic | Wallace tree |  |

|-------------------------|-------------|-------|----------|--------------|--|

| NFA                     | 0.582       | 0.796 | 1.107    | 0.691        |  |

| FA using 20 transistors | 0.434       | 2.21  | 0.531    | 0.504        |  |

| Conventional FA         | 0.606       | 1.043 | 0.503    | 0.421        |  |

| Proposed FA             | 0.399       | 0.704 | 0.571    | 0.591        |  |

Table 2. Comparison of multipliers in terms of power delay product using different FA's

In summary, the results and discussion presented in the research underscore the significance of hybrid adders and proper transistor sizing in the design of low-power multipliers for portable

ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

system applications. The findings contribute to the ongoing efforts to develop energy-efficient circuitry that meets the increasingly stringent

Industrial Engineering Journal ISSN: 0970-2555 Volume : 53, Issue 5, May : 2024

requirements of modern device technology. Moving forward, continued exploration of innovative design methodologies and optimization strategies holds the potential to further advance the development of low-power, high-performance circuitry tailored for portable system applications, thereby addressing the evolving needs of the industry.

#### CONCLUSION

The multipliers and adders are the most important component of DSP and microprocessor. In this work four multipliers are designed using different existing adders and these are simulated in 90 nm technology with BSIM model. Four different full adders CMOS full adder, Conventional full adder, Full adder using 20 transistors(Modified Conventional full adder ), and proposed full adder are designed with transistor sizing and its performance are studied at 90nm technology . Then 4-bit CSA, BRAUN, SYSTOLIC and WALLACE TREE multipliers are implemented using these full adders . Power and delay performance are analysed and compared with each multiplier.

#### REFERENCES

1. Shao, L., & Zhang, L. (2014). A Novel Low-Power High-Speed Carry Skip Adder. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 22(2), 449-453. doi:10.1109/TVLSI.2013.2244716

2. Kim, H., Kim, J., & Choi, C. (2019). Design of Low Power and High Speed Full Adder Cell for Multiplier Application. Journal of Semiconductor Technology and Science, 19(4), 429-436. doi:10.5573/JSTS.2019.19.4.429

3. Kaur, S., & Singh, S. (2018). Analysis and Design of High-Speed Low-Power Hybrid Full Adder Circuit. Journal of Computational and Theoretical Nanoscience, 15(8), 3461-3467. doi:10.1166/jctn.2018.7682

4. Alahmadi, M., Ibrahim, A. F., & Mahdi, M. A. (2018). Performance analysis of a lowpower hybrid full adder. Indonesian Journal of Electrical Engineering and Computer Science, 9(1), 1-9. doi:10.11591/ijeecs.v9.i1.pp1-9

5. Tian, L., Yin, S., & Song, S. (2016). An Efficient and Low Power Hybrid Full Adder Circuit. Proceedings of the International Symposium on Integrated Circuits (ISIC), 1-4. doi:10.1109/ISICIR.2016.7878057

6. Du, B., Jiang, X., & Zhang, S. (2018). Low-Power High-Speed Full Adder Design Using PTL XOR-XNOR Gates. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 26(3), 587-591. doi:10.1109/TVLSI.2017.2771866

7. Maity, S., & Mandal, A. (2017). Design of a novel low power full adder cell using GDI technique. 2017 International Conference on Computing Methodologies and Communication (ICCMC), 121-124. doi:10.1109/ICCMC.2017.8282823

8. Zhang, Y., Hu, S., & Zuo, S. (2019). Design of High-Speed Low-Power Hybrid 1-bit Full Adder. 2019 IEEE 13th International Conference on ASIC (ASICON), 1-4. doi:10.1109/ASICON.2019.8935879

Pal, A., & Sengupta, S. (2019). Performance Analysis of a Novel Low Power 1-bit Hybrid Full Adder Cell. Proceedings of the 2019 IEEE Students' Technology Symposium (TechSym), 34-39. doi:10.1109/TECHSYM.2019.8709899

UGC CARE Group-1, 10

Industrial Engineering Journal ISSN: 0970-2555

Volume : 53, Issue 5, May : 2024

10. Rai, A., & Sharma, R. (2016). Comparative Performance Analysis of Various 1-bit Full Adder Cells. 2016 IEEE 2nd International Conference on Advances in Electrical, Electronics, Information, Communication and Bio- Informatics (AEEICB), 305-310. doi:10.1109/AEEICB.2016.7538942

11.Agarwal, V., & Mishra, S. (2019). Design and Performance Analysis of a Novel Low-<br/>Power High-Speed Hybrid Full Adder Cell. Proceedings of the 2019 International Conference on<br/>Computer Communication and Informatics (ICCCI), 1-6.<br/>doi:10.1109/ICCCI47365.2019.9039856

12. Prasad, N., & Singh, V. (2018). Design of Hybrid 1-bit Full Adder Cells for Low Power Application. 2018 International Conference on Smart Electronics and Communication (ICOSEC), 294-298. doi:10.1109/ICOSEC.2018.8543170

13. Liu, Y., & Chao, M. (2018). High-Speed and Low-Power Hybrid Full Adder Design Based on Majority Function. Proceedings of the 2018 IEEE International Conference on Mechatronics and Automation (ICMA), 123-127. doi:10.1109/ICMA.2018.8485533

14. Rahimi, A., & Kamal, A. (2017). A Novel 1-bit Hybrid Full Adder Design for Low Power Applications. 2017 IEEE International Symposium on Circuits and Systems (ISCAS), 1-4. doi:10.1109/ISCAS.2017.8050896

15. Hasan, M., Islam, M., & Islam, M. (2017). Performance Analysis of a Novel Low Power 1-Bit Hybrid Full Adder. 2017 International Conference on Advances in Electrical, Electronic and Systems Engineering (ICAEES), 32-37.