Industrial Engineering Journal ISSN: 0970-2555

Volume : 52, Issue 5, May : 2023 EFFICIENT DESIGN OF FIR FILTER USING VEDIC SUTRAS

E. Jagadeeswara Rao<sup>1</sup>, J. Ankitha<sup>2</sup>, B. Preethi<sup>3</sup>, A. Asha Shinee<sup>4</sup>, A. Vaishnavi<sup>5</sup>

UG Students <sup>2,3,4,5</sup>, Department of Electronics and Communication Engineering, Vignan's Institute of Engineering for Women

**E. Jagadeeswara Rao<sup>1</sup>**, Assistant Professor, Department of Electronics and Communication Engineering, Vignan's Institute of Engineering for Women

#### ABSTRACT

Finite Impulse Response (FIR) filters are most widely used in communication, audio and other signal processing applications. Having a Fast and suitable multiplier in FIR filter plays a major role, as we know that multiplication operation is one of the most important elementary operations, which finds its place in the implementation of various algorithms in many applications. In present days, the demand for faster and power efficient algorithms has been increased the need for faster and power efficient multiplication is used more frequently. The multiplication method proposed ancient Indian texts known as Vedas. Vedic multiplier which is derived using different Vedic sutras, which helps in efficient multiplications. This work combines mainly two sutras namely Urdhvatiryagbhyam, Nikhilam along with Karatsuba algorithms to form Hybrid multiplier to carry out multiplications .

### INTRODUCTION

FIR (finite impulse response) filters are generally chosen for applications where linear phase is important and a decent amount of memory and computational performance are available. They have a widely deployed in audio and biomedical signal enhancement applications [1]. In other applications, the FIR filter circuit must act as a low power circuit that operates at moderate sample rates [2]. The structure of the multiplier circuit also affects the resultant power consumption and speed. Choosing multipliers with more hardware breadth rather than depth would not only reduce the delay, but also the total power consumption.

#### LITERATURE SURVEY

[1]A Low power and low area VLSI implementation of Vedic design FIR filter for ECG signal denoising was presented by MSumalatha etal.,(2019). In this paper, Vedic design-carry look ahead Adder FIR filter is designed using Urdhva Tiryagbhyam sutra. Significance of multiplier in FIRfilter is much more improved by using Vedic multiplier. The sutra used in this paper is Urdhva Tiryagbhyam, which works based on "vertically and crosswise" approach. In PE, Vedic multiplier is used to perform the multiplication operation which helps to reduce the hardware utilization. The optimal CLA adder is also used to perform the FIR filter. Finally, the process speed and area are improved in this method. But the design becomes more complex as the size of the numbers to be multiplied increases.

[5]Design and Evaluation of a FIR Filter Using Hybrid Adders and Vedic Multipliers was proposedbyJuthiFarhanaSayedetal.,(2021)[5].HereauthordesignedFIRfilterusingaVedic

multiplier, overall power consumption is reduced using this design, yet it is observed that FIR filter is lessreliable and design layout is complex.

[6]A Modified Binary Multiplier Circuit Based on Vedic Mathematics was presented by Shamim Akhteretal.,(2019).In this paper, an efficient novel technique is presented for binary multiplier circuits based on Vedic mathematics. It is proved from the synthesis results that the proposed technique is much efficient in terms of delay and LUT requirements. The proposed technique can be extended for a larger bit size. But Performance of multiplication can be improved in terms of speed.

[7]Design and performance comparison of adiabatic 8-bit multiplier was proposed by H.V. RavishAradhya et al.,(2016). In this work, Vedic-Dadda hybrid multiplier, which replaces Wallace

UGC CARE Group-1,

Industrial Engineering Journal

ISSN: 0970-2555

Volume : 52, Issue 5, May : 2023

compression with Vedic multiplier dissipates lesser power, compared to Wallace-Dadda hybrid multiplier. 8-bit Vedic multiplier proves to be an optimized design with respect to power, delay, and area for 8-bit multiplication.

In this Literature survey, we have encountered Various approaches that are utilized by researchers to apply these Vedic sutras, and algorithms. Yet, they have failed to overcome few drawbacks due to applying only one sutra which is not flexible to all size of multiplicands, which can achieved by using alternative efficient multiplier using Vedic sutras employed at different levels of the designs.

### **PROPOSED DESIGN**

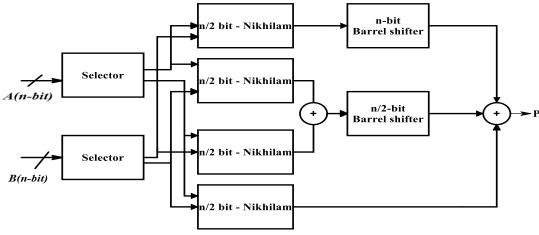

Fig 1: Hybrid Multiplier Using Nikhilam Sutra

The Proposed block diagram is designed using the following algorithm, in order to select the bits selectors are used and to shift the bits n-bit and n/2-bit Barrel shifters are used in the design of Hybrid multipliers

$\mathbf{P} = \mathbf{2^{n}}(\mathbf{A_{H}B_{H}}) + \mathbf{2^{n/2}}(\mathbf{A_{H}B_{L}} + \mathbf{A_{L}B_{H}}) + \mathbf{A_{L}B_{L}}$

## **4 RESULTS AND DISCUSSIONS**

The proposed design is simulated in Xilinx Vivado 2018.1

| Name                                    | Value | 10,999,998 ps |

|-----------------------------------------|-------|---------------|

| > 🐭 x1[7:0]                             | 05    | 0.5           |

| > 🐭 x2[7:0]                             | 03    | 03            |

| > 🐭 x3[7:0]                             | 04    | 04            |

| > 🐭 x4[7:0]                             | 03    | 0.2           |

| > 🐭 x5[7:0]                             | 02    | 02            |

| > 📲 x6[7:0]                             | 05    | 0.5           |

| > 🐭 x7[7:0]                             | 01    | 0.1           |

| > 🐭 x8[7:0]                             | 06    | 06            |

| > 🐭 m1[7:0                              | 02    | 20            |

| > 😻 m2[7:0                              | 02    | 02            |

| > 👐 m3[7:0                              | 01    | 0.1           |

| > 🐭 m4[7:0                              | 03    | 0.3           |

| > 👐 m5[7:0                              | 02    | 20            |

| > 👐 m6[7:0                              | 03    | 03            |

| > 👐 m7[7:0                              | 02    | 02            |

| > 👐 m8[7:0                              | 01    | 01            |

| > MP p[15:0]                            | 56    | 56            |

| > <b>w1[:0</b>                          | 000a  | 000a          |

| > 😻 w2[:0                               | 0006  | 0006          |

| > • • • • • • • • • • • • • • • • • • • | 0004  | 0004          |

| > w4[:0                                 | 0009  | 0009          |

| > <b>w</b> 5[:0                         | 0004  | 0004          |

| > 😻 w6[:0                               | 0001  | 000 #         |

| > 😻 w7[:0                               | 0002  | 0002          |

| > wa[:0                                 | 0006  | 0006          |

| > <b>a1[:0</b>                          | 0010  | 0010          |

| > "# a2[:0]                             | 0014  | 0014          |

Fig 2: Simulation results of proposed design

The simulation results of proposed designs are compared with the previous designs in the following table

## Table 1: Comparison of different FIR Filter designs

Industrial Engineering Journal

ISSN: 0970-2555

Volume : 52, Issue 5, May : 2023

| FIR Filter Design | Power(mW) | Area<br>(No of LUT'S) | Delay(nS) |

|-------------------|-----------|-----------------------|-----------|

| UT                | 22.636    | 876                   | 32.867    |

| NIK               | 36.615    | 878                   | 28.873    |

| KARAT             | 25.547    | 675                   | 25.678    |

| Prop_NIK          | 28.657    | 567                   | 26.768    |

We can observe the performance in the Proposed designs have been improved compared to the existing designs .The power consumption in Proposed design is reduced with minimum reduction in area with moderate delay.

# **CONCLUSION:**

In conclusion, the performance of FIR filters can be enhanced using the Urdhva Tiryakgbhyam sutra, Nikhilam sutra and Karatsuba algorithm. The computational complexity of the filter can be made simpler through calculation process optimization, resulting in quicker execution times and less resource usage. Urdhva Tiryakgbhyam multiplier is used at the lowest level Nikhilam multipliers used as a building -blocks, which are combined together using the Karatsuba algorithm and this is being proposed as Hybrid multiplier gives better results compared to the existing one. Using Vedic multiplier in FIR filter improves the performance in terms of area, delay and power consumption. The Proposed hybrid Vedic multiplier using above sutras helps to improve overall performance of FIR filter, with moderate delay and reduced area. Hence, the proposed hybrid multiplier combines the advantages of all algorithms.

### **FUTURE SCOPE:**

Here we have done our work with considered sutras from the literature survey, and we can also study more in the area. The hybrid multipliers can be modified by replacing any proposed multiplier block in the design in order to further improve the performance and to reduce the complexity of the design .

#### **REFERENCES:**

1. M Sumalatha, P.V. Naganjaneyulu, K. Satya Prasad, "Low power and low area VLSI implementation of Vedic design FIR filter for ECG signal de-noising", *Science direct-Elsevier*, *Technology and Research*, Guntur, Andhra Pradesh, India, 29 august 2019.

2. Mittal, Anubhuti, Ashutosh Nandi, and Disha Yadav. "Comparative study of 16-order FIR filter design using different multiplication techniques." *IET Circuits, Devices & Systems* 11.3 (2017): 196-200.

3. Siba Kumar Panda, Ritisnigdha Das, S K Saifur Raheman, Tapasa Ranjan Sahoo, "VLSI Implementation of Vedic Multiplier Using UrdhvaTiryagbhyam Sutra in VHDL Environment: A Novelty", *IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)*, Vol.5, Issue 1, pp 17-24, Jan-Feb 2015.

4. Juthi Farhana Sayed, Bhuiyan Hasibul Hasan, Babul Muntasir, Mehedi Hasan, Farhadur Arifin, "Design and Evaluation of a FIR Filter Using Hybrid Adders and Vedic Multipliers", *IEEE*, Dhaka, Bangladesh, 07 January 2021.

5. Shamim Akhter and Saurabh Chaturvedi, Senior Member, "Modified Binary Multiplier Circuit Based on Vedic Mathematics", *IEEE* - 08 March 2019.

6. H.V. Ravish Aradhya, H R Madan, M S Suraj, Megaraj T Mahadikar, R Muniraj, Mohammed Moiz, "Design and performance comparison of adiabatic 8-bit multipliers", *IEEE* - 14 August 2016.

Industrial Engineering Journal

ISSN: 0970-2555

Volume : 52, Issue 5, May : 2023

7. Arish S, R.K. Sharma, "An efficient binary multiplier design for high-speed applications using Karatsuba algorithm and UrdhvaTiryagbhyam algorithm", *IEEE proceedings* of 2015 Global Conference on Communication Technologies, Kurukshetra, India.