ISSN: 0970-2555

Volume: 53, Issue 6, June: 2024

# DESIGN AND IMPLEMENTATION OF HIGH SPEED AND LOW AREA QCA BASED SERIAL PARALLEL MULTIPLIER

<sup>1</sup>Mrs. D. Suvarna Kumari, <sup>2</sup>Anumalisetty Shanmukhi Satyaveni, <sup>3</sup> Bugata Sandhya Rani, <sup>4</sup> Dasari Poorna Chandrika,

<sup>1</sup>Assistant Professor, <sup>2,3,4,5</sup>B.Tech, <sup>1,2,3,4,5</sup>Department of Electronics and Communication Engineering, Vignan's Institute of Engineering for Women, Duvvada, Visakhapatnam, India

#### **ABSTRACT**

This paper unveils a unique and groundbreaking design of a serial-parallel multiplier utilizing Quantum-dot Cellular Automata (QCA) technology. The plan put forth upholds a harmonious blend of serial and parallel processing techniques to achieve efficient multiplication operations. Introducing an innovative 4-bit Serial parallel multiplier framework, consisting of an excessive 229 QCA cells. The expansion leads to an 8-bit Serial parallel multiplier configuration with a whopping 470 QCA cells using XOR gate and a bit-serial adder. Leveraging the exceptional attributes of QCA, such as its high-speed and low-power features, to obtain compactness and efficiency in execution. Extensive performance scrutiny illustrates the effectiveness of this design in offering high-speed multiplication operations while keeping power consumption as well as energy dissipation at a minimum. The scalability of this design renders it suitable for incorporation into larger systems, catering to a variety of computing applications demanding effective multiplication capabilities.

# **Keywords:**

Serial-parallel multiplier(SPM), XOR gate, bit-serial adder(BSA), QCADesigner.

#### INTRODUCTION

Quantum dot cellular automata (QCA) is a promising nanotechnology for computing, based on quantum dots – tiny semiconductor particles. QCA leverages the quantum properties of these dots to perform computations, potentially enabling faster and more energy-efficient electronics compared to traditional CMOS technology. With its potential for high-density, low-power computing, QCA has garnered significant interest for applications in areas like data storage, cryptography, and beyond.

The fundamental piece of QCA tech is a QCA cell, a square nanostructure stuffed with four quantum dots, and a pair of movable electrons, who have the capability to switch their position between dots. Because of Coulomb interaction, electrons encounter mutual repulsion and positioned diagonally from each other. More strictly, an individual cell must be in any of the two energy states, called cell polarization and represented as P = +1 (binary 1) and P = -1 (binary 0)[1],[2]. Besides, in order to execute logical operations and signal propagation, semiconductor QCAs have four-phases of clocking schemes with a 90° phase shift to each other [3].

QCA technology not only offers a novel designing pragmatic but also facilitates a revolutionary computing architecture. Up-to-dates, several elementary logic gates have been successfully fabricated and tested [4][5]. Moreover, some complex designs including memory unit [6], arithmetic logic unit (ALU) [7], [8] and microprocessor [9] have been reported. However, the physical implementation of such design is not still possible because of the complex structural trade-off. More precisely, multilayer design has significant geometric complexity in terms of physical implementation. So, single-layered majority gate is designed and is considered as the best for physical implementation [10].

#### LITERATURE SURVEY

[1] Binfeng Yang and Sonia Afrooz, A New Coplanar Design of Multiplier Based on Nanoscale Quantum-Dot Cellular Automata. 2019. A new  $2 \times 2$  array multiplier circuit in QCA by employing an efficient structure of full adder is designed and implemented. The simulation results have demonstrated that the  $2 \times 2$  multiplier leads to less cell count and area as the prime designing factors.

ISSN: 0970-2555

Volume: 53, Issue 6, June: 2024

Summary: From this journal, I have considered that the concept of QCA array multiplier consists of 493 cells and 0.72 µm², area which requires more number of cells.

- [2] Iman Edrisi Arani and Abdalhossein Rezai, Novel circuit design of serial parallel multiplier in quantum-dot cellular automata technology.2018. A novel serial-parallel QCA multiplier circuit is evaluated which is efficiently designed based on full-adder circuit and simulation results are observed. Summary: From this journal article, it is observed that 4-bit SPM utilizes 264 cells with occupancy 0.27 µm², area. This design is Computationally expensive.

- [3] K Raja Sekar, R Marshal and G Lakshminarayanan, High speed Serial parallel multiplier in Quantum-Dot Cellular Automata. 2022. SPM is an efficient circuit used in multiple applications. It has efficient clocking scheme designed without using shift registers is analyzed. Summary: From this article, 4-bit SPM consists of 237 cells with area occupancy of 0.23  $\mu$ m<sup>2</sup>, but, for this design there is no provision to store input and output.

- [4] Ali Newaz Bahar and Khan A. Wahild, Design of QCA Serial Parallel Multiplier (QSPM) with Energy Dissipation Analysis. 2020. Here, the XOR gate is modified into E shape for better simulation results and to achieve reduced in cell count along with area. Summary: From this article, it is observed that the occupancy of 229 cells and 0.243 µm², area with increased energy dissipation and time delay.

#### **EXISTING METHOD**

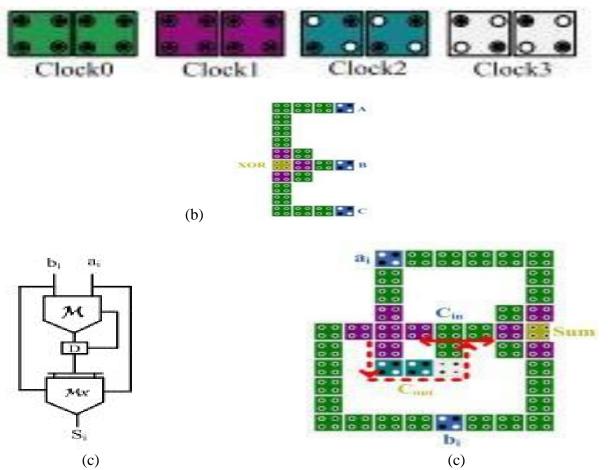

The four distinct clock zones within QCA cells signify the delay of the specific circuit design. Employing a 3-input XOR gate and a bit-serial adder with internally embedded Cin and Cout functions effectively reduces circuit complexity.

(a)

Fig: (a) clock zones (b) 3-input XOR gate (c) schematic diagram of the bit-serial adder

ISSN: 0970-2555

Volume: 53, Issue 6, June: 2024

$$Sum = a_i b_i C_{in} + a_i \overline{b_i} \overline{C_{in}} + a_i b_i \overline{C_{in}} + \overline{a_i} \overline{b_i} C_{in}$$

$$= M(\overline{M}(a_i, b_i, C_{in}), M(a_i, b_i, \overline{C_{in}}), C_{in}) \qquad \dots eq(i)$$

$$C_{out} = M(a_i, b_i, C_{in})$$

....eq(ii)

Simulation results were thoroughly analyzed. Leveraging the XOR gate and adder.

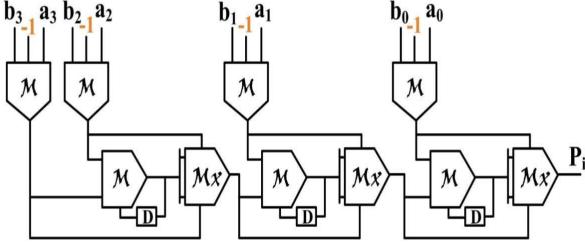

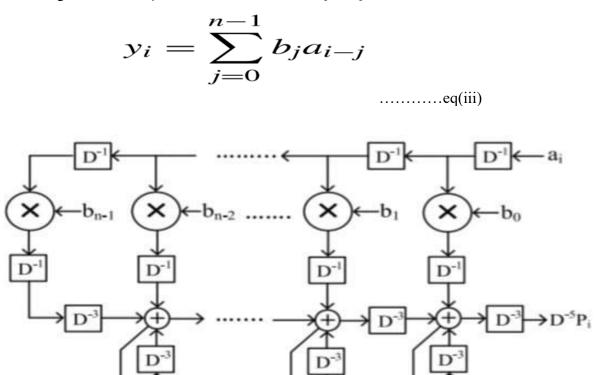

Figure.1. Schematic diagram of 4-bit SPM

In this setup, we utilize different components: M for Majority gate, Mx for Multiplexer designed with XOR gate and adder, and D for delay. The operation involves a 4-bit input represented by 'ai' and 'bi' with a polarization of '-1', executing a serial parallel multiplier operation, with the output obtained sequentially as 'Pi'.

Figure.2. A 4-bit SPM QCA design

A 4-bit Serial parallel multiplier is engineered, considering parameters such as cell count, area and energy dissipation. The below figure represents the binary output of 4bit SPM.

ISSN: 0970-2555

Volume : 53, Issue 6, June : 2024

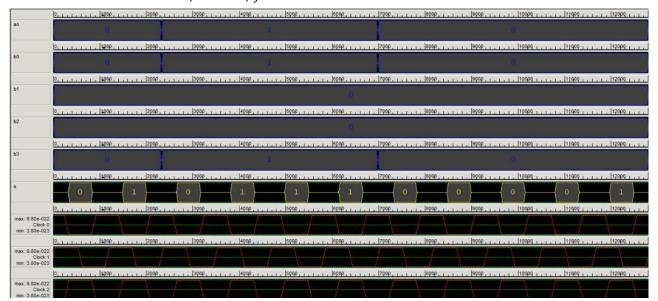

Figure.3. Simulation results of 4-bit SPM

#### PROPOSED METHOD

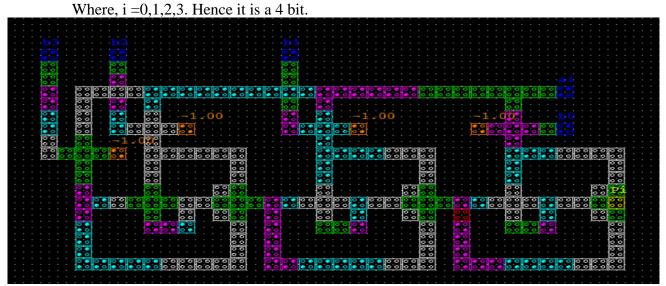

To construct the proposed multiplier network, six clock zone feedback loops are employed to internally link the carry-in and carry-out. The schematic block diagram and QCA circuit design of a 8-bit SPM are depicted, with 'a' denoting the serial input, and the serial product 'Pi' emerging after 1.25 clock cycles. In this setup, the logical "AND" operation necessitates a (D-1) clock delay, while the carry-out and sum of a full adder require only two clock zones (D-2) delay. Although wires typically don't introduce clock delays, longer wire lengths may incur some delay. Additionally, to synchronize operations, signals on the top and bottom lines are delayed by one

Figure.4. Proposed SPM network for QCA

ISSN: 0970-2555

Volume: 53, Issue 6, June: 2024

clock cycle. According to the no., of bits the design increases the delays to acquire the particular simulation result accurately.

#### THE DESIGN STRUCTURE OF THE SPM

The design structure of an 8-bit serial-parallel multiplier employs cells distributed across four clock zones, each representing a distinct delay. These clocks cycle through four states: switch, hold, release, and relax.

During the switch state, QCA cells actively transfer charge or information, performing computational tasks such as logic gates or memory functions by manipulating quantum states. In the hold state, QCA cells maintain their current charge or information without actively transferring it, crucial for retaining data during intermediate computations. The release state involves a controlled discharge of charge or information from the QCA cell, occurring after a computational operation or as part of a data transmission process. Finally, the relax state sees the QCA cell returning to its stable or equilibrium state after completing a computational operation or releasing charge. This ensures the stability of the QCA array, preparing it for subsequent operations at the nanoscale level. QCA wire used in design process such as Low Power Consumption: Nowadays, QCA wires offer really low power consumption compare to traditional CMOS technology, making them really attractive for energy-efficient designs. They work amazingly well.

High-Speed Operation: QCA wires can operate at high speeds, enabling really rapid data transmission and processing, which is super essential for modern computing applications.

Small Size: QCA wires can be fabricated at the nanoscale, allowing for the creation of compact and densely integrated circuits. This small size is particularly advantageous for applications where space is limited, like in portable devices or embedded systems.

Parallel Processing: QCA wires enable parallel processing, where multiple operations can be performed simultaneously. This parallelism can significantly enhance the overall performance of the system, especially for tasks that involve large amounts of data processing.

Scalability: QCA wires are inherently scalable, meaning that they can be easily scaled down to smaller sizes as technology advances. This scalability ensures that QCA-based designs remain relevant and competitive in the ever-evolving field of nanoelectronics.

SPM is designed with each clock delay of 1.25 in the order of clocks zones and the output is received in a sequential manner and the simulation result is analyzed and the particular multiplication operation is performed with minimal cell count of 470 with 0.498  $\mu$ m<sup>2</sup>, area which is a efficient and less complex. Hence, the delay is reduced simultaneously with the reduction of cells.

#### **RESULT ANALYSIS**

The schematic circuits of the serial parallel multiplier discussed above are simulated in QCADesigner tool using QCA technology. The 8-bit SPM is simulated with the total simulation time 7.00e-011 sec, the clock amplitude factor 2.0, relative permittivity 12.9. The cell count, area, latency and crossover type of the different multipliers are compared for best utilization. The high-speed, low power and less energy dissipation SPM is designed and used in distinct applications.

ISSN: 0970-2555

Volume : 53, Issue 6, June : 2024

# Figure.5. Proposed 8-bit SPM

This multiplier is used in applications such as digital signal processing, image processing, cryptography, and communication systems. They are particularly useful when dealing with large numbers or complex computations where parallel processing can significantly speed up the operation.

Table.1. Simulation parameters of coherence vector engine

| Parameter              | Value<br>18 nm          |  |

|------------------------|-------------------------|--|

| Cell Width             |                         |  |

| Cell Hight             | 18 nm                   |  |

| Relative Permittivity  | 12.9                    |  |

| Clock High             | 9.8 e <sup>-22</sup> J  |  |

| Clock Low              | 3.8 e <sup>-23</sup> J  |  |

| Clock Amplitude Factor | 2                       |  |

| Time Step              | 1.00 e <sup>-11</sup> s |  |

| Relaxation Time        | 1.00 e-16 s             |  |

| Simulation Time        | 80 e <sup>-12</sup> s   |  |

| Radius of Effect       | 80 nm                   |  |

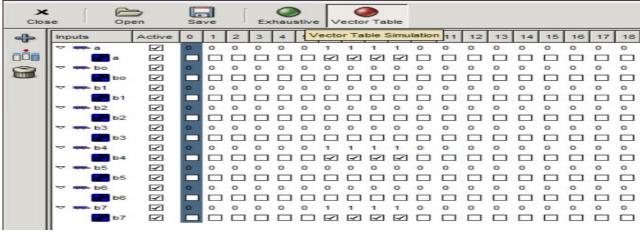

Fig:(d)

Fig:(e)

Figure: (d), (e) Represents the vector input table for 8-bit SPM and simulation result of it.

| Table 2: Comparative A | Analysis of the proposed | 8-bit SPM with others |

|------------------------|--------------------------|-----------------------|

|------------------------|--------------------------|-----------------------|

| Word    | Multiplier      | Cell count | Area(µm²) | Latency (clock cycle) | Crossover Type |

|---------|-----------------|------------|-----------|-----------------------|----------------|

| 4 - bit | Cho et al. [7]  | 406        | 0.493     | 1                     | Multilayer     |

|         | Zhang et al [8] | 329        | 0.299     | 1                     | Multilayer     |

|         | Ali et al [1]   | 229        | 0.243     | 1.25                  | Coplanar       |

| 8-bit   | Cho et al. [7]  | 903        | 0.996     | 1                     | Multilayer     |

|         | Zhang et al [8] | 749        | 0.736     | 1                     | Multilayer     |

|         | Ali et al [1]   | 529        | 0.557     | 1.25                  | Coplanar       |

|         | Proposed        | 470        | 0.498     | 1.25                  | Coplanar       |

# **CONCLUSION**

In this paper, a new expandable 8-bit SPM using XOR gate and bit-serial adder (BSA) is presented. To validate the efficiency of the proposed BSA module, various bit size multipliers have been

# OF INDUSTRALE ENGLY

# **Industrial Engineering Journal**

ISSN: 0970-2555

Volume: 53, Issue 6, June: 2024

presented and evaluated. The simulation results show that the reported BSA and SPM operate with higher efficiency and achieved a notable improvement in terms of cell count and occupied area. In addition, the proposed SPM has 80% lower design cost over the existing design, which demonstrates the advantage of the proposed design.

#### REFERENCES

- 1. Ali Newaz Bahar and Khan A. Wahild (2020)," Design of QCA Serial Parallel Multiplier (QSPM) with Energy Dissipation Analysis, "IEEE Trans. on Circuits Syst. II, Brief, vol:67, Issue:10, October2020.

- 2. N. G. Anderson and S. Bhanja, Field-Coupled Nanocomputing (LNCS8280). Heidelberg, Germany: Springer-Verlag, 2014.

- 3. I. Amlani, A. O. Orlov, G. Toth, G. H. Bernstein, C. S. Lent, and G. L. Snider, "Digital logic gate using quantum-dot cellular automata," Science, vol. 284, no. 5412, pp. 289–291, 1999.

- 4. R. P. Cowburn and M. E. Welland, "Room temperature magnetic quantum cellular automata," Science, vol. 287, no. 5457, pp. 1466–1468,2000.

- 5. C. S. Lent, B. Isaksen, and M. Lieberman, "Molecular quantum-dot cellular automata," J. Amer. Chem. Soc., vol. 125, no. 4, pp. 1056–1063,2003.

- 6. M. Kianpour and R. Sabbaghi-Nadooshan, "A novel quantum dot cellular automata X-bit  $\times$  32-bit SRAM," IEEE Trans. Very Large Scale Integer. (VLSI) Syst., vol. 24, no. 3, pp. 827–836, Mar. 2016.

- 7. H. Cho and E. E. Swartzlander, "Adder and multiplier design in quantum-dot cellular automata," IEEE Trans. Comput., vol. 58, no. 6, pp. 721–727, Jun. 2009.

- 8. Y. Zhang, H. Lv, H. Du, C. Huang, S. Liu, and G. Xie, "Modular design of QCA carry flow adders and multiplier with reduced wire crossing and number of logic gates," Int. J. Circuit Theory Appl., vol. 44, no. 7, pp. 1351–1366, 2016.

- 9. K. Walus, M. Mazur, G. Schulhof, and G. A. Jullien, "Simple 4-bit processor based on quantum-dot cellular automata (QCA)," in Proc. IEEE Int. Conf. Appl. Specific Syst. Archit. Processors, 2005, pp. 288–293.

- 10. C. R. Graunke, D. I. Wheeler, D. Tougaw, and J. D. Will, "Implementation of a crossbar network using quantum-dot cellular automata," IEEE Trans. Nanotechnol., vol. 4, no. 4, pp. 435–440, Jul. 2005.