Industrial Engineering Journal ISSN: 0970-2555

Volume : 52, Issue 7, No. 1, July : 2023

# DESIGN AN ADDRESS PREDICATED SRAM ARCHITECTURE FOR HIGH SPEED AND FAULT FREE MEMORY COMPUTING

Dr.S.Koteswari, Professor & Head, Department of ECE, Pragathi Engineering College, Suramapalem, Kakinada. Permanently Affiliated to JNTUK, Andhrapradesh <u>eshwari.ngr@gmail.com</u>

Radhamadhuri Indukuri, Assistant Professor, Department of Mathematics &Humanities, S R K R Engineering College, Affiliated to JNTUK, Andhrapradesh <u>radhamadhuri.indukuri@gmail.com</u>

Dr.M. Aravind Kumar, Professor & Principal, Department of ECE, West Godavari Institute of Science and Engineering Affiliated to JNTUK, Andhrapradesh <u>drmaravindkumar@gmail.com</u>

**ABSTRACT:** This paper is based on an address-based SRAM architecture is used to provide memory computation at high speed and without errors. This project's primary goals are to shorten delays and enhance system performance. BIST tests the input initially before sending the data to the SRAM control circuit block. CRC will find and fix any flaws in the data it receives, providing reliable information. Data addresses are decoded by the address control unit using the row and column decoders. The data is decoded using a row decoder and a column decoder using a column format. The row and column at last the row and column data will finally be stored in an SRAM array. There will be read and write operations on this data. Xilinx technology is being used to replicate this. The results of the simulation show that an effective output in terms of delay and area is attained

**KEYWORDS**: Row Decoder, Column Decoder, CRC (Cyclic Redundancy Check), Amplifier, Static Random Access Memory (SRAM), read bit-line (RBL), SRAM bit cells.

# **I.INTRODUCTION:**

Static Random Access Memory (SRAM) occupies a sizable portion of a system on a chip (SoC) and significantly contributes to the SOC's overall performance and area. Memory configuration engineers intend to place however many cells would be prudent per segment to permit sharing of auxiliary hardware because region is a significant consideration when designing circuits [1]. The inability of the standard 6T and 8T cells to function in longer lengths severely restricts their functionality. Scaling has been used in recent years to produce the improved CMOS device [1]. Operating low power circuits is a crucial parameter for today's integrated circuits. the use of portable battery-powered electronics like small radios, smart phones, and portable computers declines .The desire for longer battery life, which is becoming more widespread and mind-boggling, necessitates the hunt for new technologies and circuit systems that provide better and longer working conditions. Additionally, reducing power dispersion is evolving as a crucial fundamental problem for non-compact applications [1]. It is also crucial to have a basic event in order to meet the continual execution of sophisticated programmers in computers. However, as technology scales up, spilling currents become a significant proponent of the independent power distribution more mind amazed and common the interest for expanded battery life requires to search out new innovations and circuit system.

That gives superior and long operational circumstances. Applications However, the sub threshold overflowing currents grow exponentially. This increased leaking and decreased supply voltage result in circuits operating unreliable and securely. In order to describe digital CMOS circuits with reduced

Industrial Engineering Journal

ISSN: 0970-2555

Volume : 52, Issue 7, No. 1, July : 2023

dynamic and spilled power, a worthy deferral, and a noisy edge, an active is made in this suggestion. Three different digital CMOS circuits are explored and introduced for the purpose of using various power reduction techniques [3].

The developing interest of compact battery worked frameworks has made strong skilledprocessorsaneed.Forapplicationslikesuitablefiguringactiveproductivitytakestopgenerallyneed.The seinsertedframeworks need continued charging of their batteries. The issue is gradually extreme in the remote sensor systems which are sent for checking then aural parameters [4].

Memory structures have become in separable piece of current VLSI frameworks. Semiconductor memory is directly simply remaining solitary memory chip as well as a vital piece of complex VLSI frameworks. The dominating model for streamlining is regularly to pressing however much as memory as could reasonably be expected in a given region. This pattern toward compact figuring has prompted power issues in memory .The pattern of scaling of gadget sizes, low limit voltage, and ultra-slim gate oxide have progressively been tested by fluctuation, and along these lines, by depend ability related issues.

SRAM's effect has gotten particularly significant because of the rise of battery fueled convenient gadgets and low force sensor applications. Most SRAM plan exertion has been directed to encourage voltages calling and improving yield. The traditionally actualized six transistor (7T) cell in SRAMs permits high thickness, bit-interleaving and quick differential detecting however experiences half-select security, read-upset depend ability, and clashing per use and compose measuring. Past endeavors to unravel these issues have incorporated the usage of help met Enhancements, or innovative turns of events Most SRAM shared developed using multi VDD biasing to achieve low power consumptions and low delays with the use of Voltage level shifters.

# **II. EXISTINGMETHOD:**

Although the productivity of current procedure stores puts a strain on the force utilization, the force utilization of SRAMs is discussed. Finally, the five-transits orbit-cell is presented as an intriguing other choice, albeit in a configuration known as 5T-Portless.Because of its superiority, static arbitrary access memories (SRAM) are most frequently used; a chip may have up to 70% of SRAMs in a transistor count or region. The semiconductor industry is characterized by a push for increased corporate and a steadily shrinking size; as a result, the development of an inventive centre is becoming more difficult and expensive.

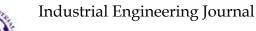

The first SE-10T SRAM cell of the introduced bit cell is appeared in Fig.1.The 6Tcell now has a 4T read port that is built of an inverter and a gearbox door (TG), which restricts the read route from inner capacity hubs. Hub Q Band drives the read bit line (RBL) through TG (M8 and M9), which is constrained by two integral read word lines (WLs). The inverter (M6 and M7) is driven by this. During a read action, this SE-10T cell can totally charge or release RBL by itself. Therefore, setting up a pre charge circuit for RBL is completely unnecessary.

ISSN: 0970-2555

Volume : 52, Issue 7, No. 1, July : 2023

#### Fig.1: SCHEMATIC OF EXISTING DESIGN

The essential level of unwavering quality becomes difficult to satisfy as memory size increases. For the SRAMs, this causes them to be the faintest in modern innovation hubs.

The for utilization increases as CMOS technology progresses. Low edge voltages are needed for CMOS scaling in conjunction to extremely thin gate oxides to maintain the current drive and keep an eye on limit voltage variations while dealing with short-channel effects. Low limit voltage causes the sub edges pill age current to increase exponentially, which increases the static force utilization. Massive piece lines' capacity can be charged or discharged, which indicates a significant portion of intensity usage during composition or reading jobs. This refers to the dynamic force.

#### **III. PROPOSEDMETHOD:**

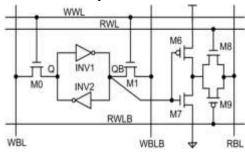

The below figure (2) shows the architecture of proposed system. Initially input is tested unit BIST and transfers the data to SRAM control circuit block. If there are any errors in obtained data CRC will detect and correction and gives the accurate data. Address control unit decodes address of data in two ways they are row decoder and column decoder. Row decoder decodes the data in row format and column decoder will decodes the data in column format. At last the row and column data will be saved in SRAM array memory. From this data will perform read and write operations.

Fig.2: PROPOSED METHOD

# 1. SRAM

The pressing thickness of integrated circuits (ICs) is constantly increasing and the segment or transistor

Industrial Engineering Journal

ISSN: 0970-2555

Volume : 52, Issue 7, No. 1, July : 2023

size is decreasing due to the semiconductor industry's rapid development. Static Random-access memory (SRAM) is a crucial component of modern electronic devices. A base estimated memory cell is enticing for achieving higher coordination thickness of SRAM, but this essentially expands spillage current. Backup spillage is a key component of adding to current spillage in lesser innovation. Because versatile handheld devices like wises can be used in reserve mode for long periods of time, spillage while in this mode is also a real concern because it shortens the battery's life. The circuit is operated at a lower flexible voltage in Complex Metal Oxide Semiconductor (CMOS) technology to reduce leakage current, although doing so slows down the circuit's speed.

By using transistors with lower threshold voltages, postponement can be reduced; nevertheless, this boosts the sub-edge spillage current. There are many requirements, and substantial development is necessary to build a memory cell with less backup spilling and greater solidity. Smaller size and lower voltages seriously impair the stability of information in cells. The stability of SRAM depends on the static, which in turn depends on various other cell borders.

# 2. CYCLIC REDUNDANCY CHECK:

The main intent of cyclic redundancy check is to detect the errors and correct the errors.

# 3. ROWADDRESS

These are the set of cells that generate the word line signals from the word decoders .This structure takes a set of n address lines and generates word lines .At most; one of the word lines is activate time.

# 4. COLUMN ADDRESS

Column address select particular bit lines for being connected to sense amplifiers. This is accomplished either by sensing every bit line and getting a few of them out or by using pass gates to enable them to a few sense amplifier inputs

# RESULTS

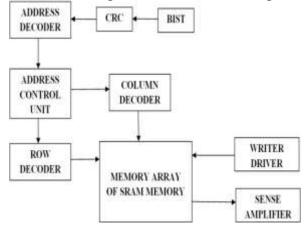

The below figure (3) shows the RTL Schematic of proposed system.

Fig.3: Rtl Schematic Of Proposed System

Fig.4: Technology Schematic Of Proposed System

The below figure (5) shows the output wave form of proposed system.

UGC CARE Group-1,

Industrial Engineering Journal ISSN: 0970-2555

Volume : 52, Issue 7, No. 1, July : 2023

Fig.5: Output Wave Form of Proposed System

#### **IV.CONCLUSION:**

As a result, an address-based SRAM architecture was designed and put into use for high-speed, faultfree memory computation. Row and column decoding are the two methods by which the address control unit decodes data addresses. Read and write operations will be made on this data. Utilizing Xilinx technology, this is simulated. From the outcomes of the simulation, it can be seen that effective'

#### **V.REFERENCES:**

- [1] ShouryaGupta,Benton H.Calhoun,"Low-PowerNear-Threshold10TSRAMBit Cells With Enhanced Data- Independent Read Port Leakage for Array Augmentation in 32-nmCMOS",1549-8328©2018IEEE.

- [2] Chinmay Sharma and Varun Chhabra, "Design of SRAM array using Reversible logic for an efficient SoC design", IEEE, 2017, ISBN 1-5386-1887-5, \$17.00.

- [3] Colin David Karat and Soorya Krishna K, "Design of SRAM Array Using 8T Cell for Low Power Sensor Network", 2015 IEEE, 978-1-4799-9991-0/15/\$31.00

- [4] P.RaikwalDesign and Analysis of Low Power Single Ended 8T SRAM ARRAY (4x4) at 180nm Technology, by V. Neem A. Verma, 978-1-5090-4620-1/16, \$31.00 (2016) IEEE.

- [5] "Design of Low Leakage SRAM Bit-Cell and Array", MSRIT, BANGALORE, India, 21-22 NOVEMBER 2014 by Shashank Ranganath, Shankara narayana Bhat M., and Alden C. Fernandes.