ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

## REVERSIBLE LOGIC GATES AND ITS APPLICATION: A COMPREHENSIVE SURVEY

Sakshi Garad, Electronics & Telecommunication, MESCOE, Pune, India.

sakshi7pgarad@gmail.com

Vinay Khochare, Electronics&Telecommunication, MESCOE, Pune, India.

vinay.khochare18@gmail.com

Pranav Bhalerao Electronics & Telecommunication, MESCOE, Pune, India.

Pranavb1502@gmail.com

#### **Abstract:**

The performance requirement increases with the application of computers in domains like artificial intelligence, machine learning, data science, big data, etc. The power consumption increases with an increase in performance. High power consumption, heat dissipation, unable to meet size requirements, and operational speed confines the further development of CMOS technology for circuit designing. Reversible logic is the key to entering into the new era of incredibly compact electronic computational devices with ultra-low power consumption. Reversible logic is an emerging field that is gaining interest as it can overcome the limitations of CMOS technology. It has been proved that any Boolean function can be implemented using reversible gates. This article gives a brief overview of reversible logic gates that have been discovered to date. It also discusses the circuits built using reversible logic gates.

**Keywords:** Reversible logic gates, reversible computing, power dissipation, garbage outputs, quantum cost, Application of Reversible logic gates, VLSI.

## INTRODUCTION:

As predicted by Gordon Moore in 1960, the number of transistors on a chip doubles on average every one and a half years. This is popularly known as 'Moore's Law' [1]. The reduction in feature size has led to several implementation and operational difficulties. It is difficult for CMOS technology to continue with the required level of growth. Since the power consumption of CMOS circuits increases with clock frequency and frequency determines computation speed and performance. An increase in performance also increases power Consumption. The challenge is the unsustainable relationship between power consumption versus performance.

According to Landauer [2][3]the amount of energy dissipated for every irreversible bit operation is at least KTln2 joules, where K=1.3806505\*10-23m2kg-2K-1 (joule/Kelvin-1) is the Boltzmann's constant and T is the absolute temperature at which operation is performed Bennett[4] showed that energy dissipation problem is avoided with circuits built using reversible logic gates. In [5] describes the concept of reversible logic which says about the circuit going back at any point for recovering data bit. Hence there is no information that is actually lost and the heat generated during this is also very negligible [6]. Qubit is the term used to describe a single bit of information; 0 or 1; stored in an elementary unit. Any operation on the single bits can be made reversible and hence, quantum circuits and networks.

C. Younis and Knight [7] showed that some reversible circuits can be made asymptotically energy-lossless as their delay is allowed to grow

arbitrarily large. Currently, energy losses due to irreversibility are dwarfed by the overall power dissipation, but this may change if power dissipation improves. In particular, reversibility is important for nanotechnologies where switching devices with gain are difficult to build. The reversibility in computing conveys the idea that

information in the computing state is never lost and is available when needed [8].

Logical reversibility is a process in which the first step can be recovered by back-calculating the result. Physical reversibility refers to no energy dissipation of heat. Logical reversibility is achieved after physical reversibility.[9]The reversible logic gate is a logic device that has n inputs and n outputs. This helps us to distinguish between outputs and inputs, allowing us

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

to selectively recover each input from the output. A reversible circuit has 'n' inputs in which 'a' are primary inputs and 'b' are constant inputs

(a+b=n), and on the output side, there are 'm' primary outputs and 'k' garbage outputs with k+m=n. The reversible circuit is designed with a minimum number of reversible logic gates, a minimum input constant, and a minimum number of garbage outputs.

Currently, reversible logic is used to implement various combinational and sequential circuits like ALU, counters, encoders, flip flops, fault checkers, etc. This article summarizes all the reversible logic gates implemented till date by various authors, explains the working and provides the use case of each reversible logic gate.

## **BASIC PARAMETERS:**

As defined in [5][10] there are several terminologies and parameters related to reversible logics.

Constant inputs: Many Boolean functions are not reversible. Therefore, before realizing these functions, we need to transform them into reversible functions. This conversion is done by a constant input. This is the number of inputs that are held constant at 0 or 1 to synthesize a particular logic function.

Garbage Outputs: Garbage Output is the number of unused outputs in a reversible gate that are unavoidable and are important for achieving reversibility.

Relation:

inputs + constant inputs = outputs + garbage outputs.

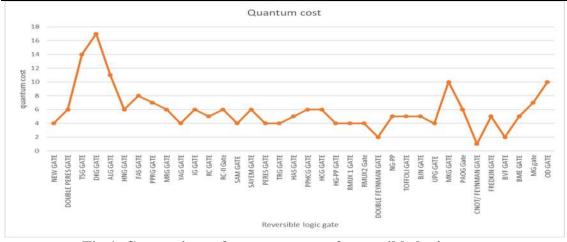

Quantum Cost: The quantum cost of a reversible circuit is the total number of 2x2 quantum primitives used to form the equivalent circuit. Some properties of quantum cost are

a.)

$$V*V = NOT$$

b.)

$$V*V+ = V+ *V = 1$$

c.)  $V+*V+ = NOT$

Delay: The delay of a logic circuit is the maximum number of gates in a path from any input line to any output line. The definition is based on two assumptions: (i)Each gate performs computation in one unit time and (ii) all inputs to the circuit are available before the computation begins.

(Mohammadi & Eshghi, 2009). [A review on reversible logic gates]

Hardware complexity: The hardware complexity determines the number of logical operations performed in the circuit, such as AND, OR, EX-OR.

Flexibility: Flexibility shows the universality of reversible logic gates. To achieve reversibility we need minimal garbage output, minimal delay, and no feedback/loops.

## **REVERSIBLE LOGIC GATES:**

## I. 2\*2 Reversible logic gates

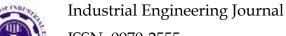

## **CNOT/ FEYNMAN GATE:**

The input vector is  $Iv=\{X,Y\}$  and the output vector is  $Ov=\{X,X \oplus Y\}$ . The first input can pass or invert the second input, hence it is called the controlled NOT gate. The quantum cost is 1. Feynman gate is used for duplication of outputs.[11]

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

## II. 3\*3 Reversible logic gates

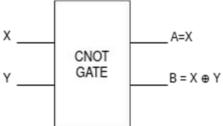

#### **TOFFOLI GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, Y, XY \oplus Z\}$ . The last bit is target bit, the rest are control bits, when control bit is 1 the target bit is inverted. The quantum cost is 5. Toffoli gate can be used to realize any function, hence it is known as universal reversible gate.[12]

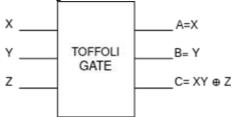

## FREDKIN GATE:

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, XY \oplus XZ, X'Z \oplus XY\}$ . The input X is mapped directly to the output A. If X=0, Y is mapped to B, Z is mapped to C. If X=1, swap operation is performed and Y is mapped to C and Z is mapped to

B. Therefore it is also known as a Controlled SWAP gate. The quantum cost is 5. Fredkin gate is used to preserve parity.[13]

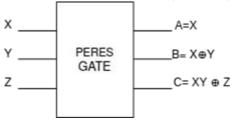

## **PERES GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, X \oplus Y, XY \oplus Z\}$ . The quantum cost is 4. TRG gate is used for implementation of a full subtractor. Peres gate can be used to realize functions like NOT, AND, NAND, XOR[12].

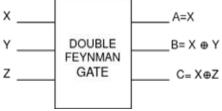

## **DOUBLE FEYNMAN GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, X \oplus Y, X \oplus Z\}$ . The quantum cost is 2. Double Feynman gate is a parity preserving gate.[14]

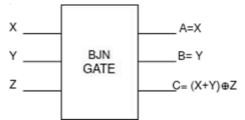

#### **BJN GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, Y, (X+Y) \oplus Z\}$ . The quantum cost is 5.[15]

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

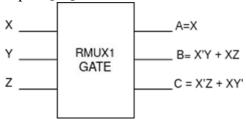

## **RMUX 1 GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, X'Y + XZ, X'Z + XY'\}$ . The quantum cost is 4. RMUX1 works as a 2:1 MUX, where X is the select line and Y&Z are the two inputs.[16]

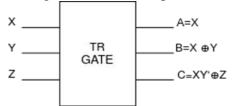

## **TRG GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, X \oplus Y, XY' \oplus Z'\}$ . The quantum cost is 4.

TRG gate is used for implementation of a full subtractor.[16]

## **NEW GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, XY \oplus Z, X'Z' \oplus Y'\}$ .[15]

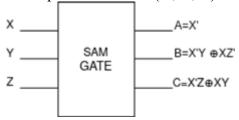

## **SAM GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X', X'Y \oplus XZ', X'Z \oplus XY\}$ . [15]

## **NFT GATE**

New fault tolerant gate is a parity preserving gate. The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X \oplus Y, YZ' \oplus XZ', YZ \oplus XZ'\}$ . [14]

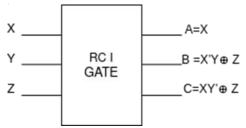

#### **RC-I GATE:**

RC-I gate is a single bit comparator circuit. The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is Ov=

$\{X, X'Y \oplus Z, XY' \oplus Z\}$ . It compares X and Y. [17]

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

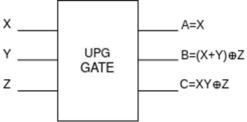

#### **UPG GATE:**

Universal Programmable Gate (UPG) can be used to implement logical functions like AND, OR, NAND and NOR. The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, (X+Y) \oplus Z, XY \oplus Z\}$ . It can perform the logical operations at low quantum cost.[16]

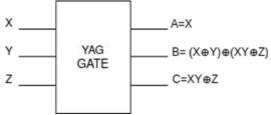

## **YAG GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, (X \oplus Y) \oplus (XY \oplus Z), XY \oplus Z\}$ . YAG is used to realize AND and OR functions.[18]

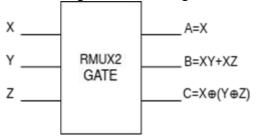

## **RMUX2 GATE:**

The input vector is  $Iv=\{X, Y, Z\}$  and the output vector is  $Ov=\{X, XY+XZ, X \oplus (Y \oplus Z)\}$ . The quantum cost of the gate is 4. In this gate X is the select line, the gate gives multiplexed output of Y and Z. [16]

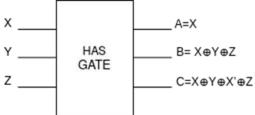

#### **HAS GATE:**

Half Adder Subtraction gate has quantum cost 5. The input vector is  $Iv=\{X,Y,Z\}$  and the output vector is  $Ov=\{X, X \oplus Y \oplus Z, X \oplus Y \oplus X' \oplus Z\}$ . HAS gate is used to implement BCD adder, carry skip BCD adder circuit, half adder and full subtractor. (Misra et al., 2015). [19]

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

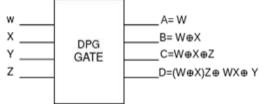

## III. 4\*4 Reversible logic gates

## **DOUBLE PERES GATE:**

The input vector is  $Iv = \{W, X, Y, Z\}$  and the output vector is  $Ov = \{W, W \oplus X, W \oplus X \oplus Z, (W \oplus X)\}$ . The quantum cost is 6. Double Peres gate is used to implement full adder. [20]

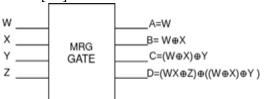

#### **MRG GATE:**

Marrison-Ranganathan gate (MRG) is a programmable gate. The input vector is  $Iv = \{W, X, Y, Z\}$  and the output vector is Ov

```

= \{W, W \oplus X, (W \oplus X) \oplus Y, (WX \oplus Z) \oplus ((W \oplus X) \oplus Y\}

```

The quantum cost is 6. MRG gate can perform 4 logical operation namely OR, NOR, XNOR and XOR.[21]

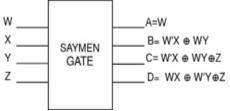

#### **SAYEM GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W,W'X \oplus WY, W'X \oplus WY \oplus Z, WX \oplus W'Y \oplus Z\}$ . The Sayem gate can be used to build reversible standard sequential circuits like T flip-flop, D flip-flop along with Feynman gate. [11]

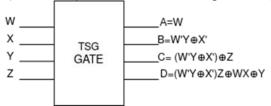

## **TSG GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W, W'Y \oplus X', (W'Y \oplus X') \oplus Z, (W'Y \oplus X')Z \oplus WX \oplus Y\}$ . TSG gate along with CNOT gate is used to implement full adder .[22]

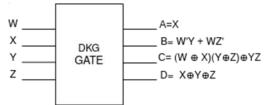

#### **DKG GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{X, W'Y+WZ', (W \oplus X)(Y \oplus Z) \oplus YZ, X \oplus Y \oplus Z\}$ . DKG gate can singly work as either a full adder or full subtractor. W is the control line, if W is set to 0 it will work as full adder and if W is set to 1 it will work as full subtractor. [23]

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

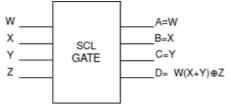

## **SCL GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W,X,Y,W(X+Y)\oplus Z\}$ . SCL gate is used to add 6 to the sum for correcting it to get the actual BCD sum.[20]

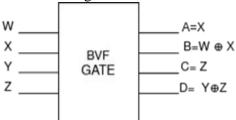

#### **BVF GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W, W \oplus X, Y, Y \oplus Z\}$ . BVF is a double XOR gate. BVF is used for extracting necessary inputs to meet the fan-out requirements.[24]

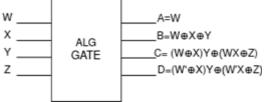

## **ALG GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W,W\oplus X\oplus Y,(W\oplus X)Y\oplus (WX\oplus Z),(W'\oplus X)Y\oplus (W'X\oplus Z)\}$ . The ALG gate can perform multiple operations like full adder, full subtractor, XOR, NAND and NOR. [22]

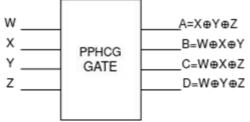

## **PPHCG GATE:**

Parity Preserving Hamming Code Generating gate is a parity preserving reversible gate. The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{X \oplus Y \oplus Z , W \oplus X \oplus Y , W \oplus X \oplus Z , W \oplus Y \oplus Z \}$ . The quantum cost is 6. PPHCG is used for achieving fault tolerance for the hamming error coding and detection.[14]

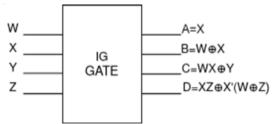

#### **IG GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{X, W \oplus X, WX \oplus Y, XZ \oplus X'(W \oplus Z)\}$  IG gate can be used to perform to perform logical operations like inverter, EX-OR, AND ,EX-NOR and OR. It is a one through gate which means one of the input variable is also the output.[14]

ISSN: 0970-2555

Volume : 52, Issue 8, No. 1, August : 2023

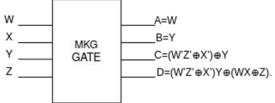

## **MKG GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W\ , Y, \ (W'Z'\oplus X')\oplus Y, \ (W'Z'\oplus X')Y\oplus (WX\oplus Z)\}$ . MKG gate is used to realize logical functions like NAND, NOT, NOR ,EX- OR, AND, EX-NOR and OR. The MKG gate is a two- through gate, which means that two of the input variables are also outputs.[25]

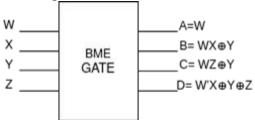

#### **BME GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W,WX \oplus Y,WZ \oplus Y,W'X \oplus Y \oplus Z\}$ . The quantum cost is 5.[19]

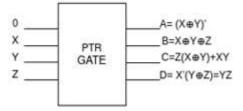

#### PTR GATE:

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{(X \oplus Y)', X \oplus Y \oplus Z, Z(X \oplus Y)+XY, X'(Y \oplus Z)=YZ\}$ . [19]

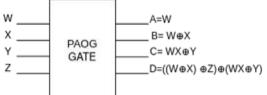

#### **PAOG:**

Peres And-Or is an extension of the Peres gate for ALU realization. The input vector is  $Iv=\{V,W,X,Y,Z\}$  and the output vector is  $Ov=\{W,W \oplus X,WX \oplus Y,((W \oplus X) \oplus Z) \oplus (WX \oplus Y)\}$ . When the PAOG is utilized as a programmable reversible logic in gate with two select inputs, it will calculate four logical calculations on those two logical outputs: OR, NOR, AND and NAND.The quantum cost is 6.[16]

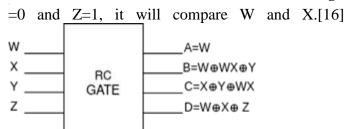

## RC GATE:

The input vector of Reversible comparator gate is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W, W \oplus WX \oplus Y, X \oplus Y \oplus WX, W \oplus X \oplus Z\}$ . The quantum cost is 5. Y and Z are the control lines when UGC CARE Group-1,

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

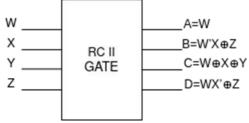

## **RC-II GATE:**

RC-II gate is a reversible sign bit comparator. The input vector of Reversible comparator gate is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W,W'X \oplus Z,W \oplus X \oplus Y,WX' \oplus Z\}$ . RC-II gate is used to compare two unsigned bits.[17]

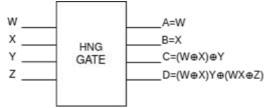

#### **HNG GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W$ , X,

$W \oplus X \oplus Y$ ,  $(W \oplus X)Y \oplus (WX \oplus Z)$ }. The quantum cost of the HNG is 6. When Z = 0, the circuit works as full adder.[16]

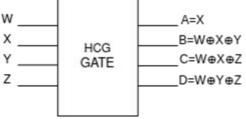

#### **HCG GATE:**

Hamming Code Generating gate (James et al., 2007) is a one-through gate which means that one of the input variables is also output.

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{X, W \oplus X \oplus Y, W \oplus X \oplus Z, W \oplus Y \oplus Z\}$ . HCG is used to implement Hamming error coding and detection circuits.[19]

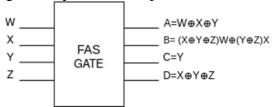

#### **FAS GATE:**

The input vector is  $Iv=\{W,X,Y,Z\}$  and the output vector is  $Ov=\{W \oplus X \oplus Y, (X \oplus Y \oplus Z)W \oplus (Y \oplus Z)X, Y, X \oplus Y \oplus Z\}$ . The gate has a quantum cost of 8. Full Adder Subtraction gate can perform the operation of full adder and full subtraction.[19]

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

## IV. 5\*5 Reversible logic gates

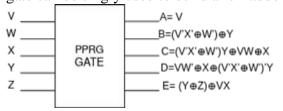

## **PPRG GATE:**

Parity preserving reversible gate is one through which means one of its inputs is also an output. It is a universal gate. The input vector is  $Iv=\{V,W,X,Y,Z\}$  and the output vector is  $Ov=\{V,(V'X'\oplus W')\oplus Y,(V'X'\oplus W')\oplus Y,(V'X'\oplus W')\oplus Y,(Y\oplus Z)\oplus VX\}$ . P2RG gate can be singly used to build a full adder and full subtractor. [26]

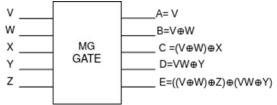

#### MG GATE:

Morrison Gate is programmable reversible logic gate. The input vector is  $Iv=\{V,W,X,Y,Z\}$  and the output vector is  $Ov=\{V,V \oplus W,(V \oplus W) \oplus X,VW \oplus Y,((V \oplus W) \oplus Z) \oplus (VW \oplus Y)\}$ . The quantum cost of the MG is 7. [16]

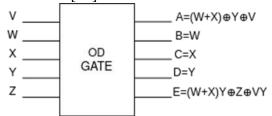

#### **OD GATE:**

The input vector is  $Iv=\{V,W,X,Y,Z\}$  and the output vector is  $Ov=\{(W+X) \oplus Y \oplus V, W, X, Y, (W+X)Y \oplus Z \oplus VY\}$ . Overflow Detection gate has quantum cost of 10. OD gate is used for overflow detection.[19].

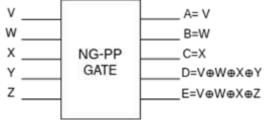

#### NG-PP:

The input vector is  $Iv=\{V,W,X,Y,Z\}$  and the output vector is  $Ov=\{V, W, X, V \oplus W \oplus X \oplus Y, V \oplus W \oplus X \oplus Z\}$ . The quantum cost of NG-PP gate is 5 (Misra et al., 2017). It is used as parity generator and parity checker circuit.[19].

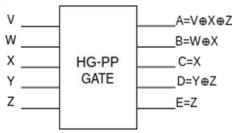

## **HG-PP GATE:**

The input vector is  $Iv=\{V,W,X,Y,Z\}$  and the output vector is  $Ov=\{V \oplus X \oplus Z, W \oplus X, X, Y \oplus Z, Z\}$ . The quantum cost of the HG-PP gate is 4.

The number of 1's in input and output are the same. HG-PP gate is used to design hamming code.[19]

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

## V. 6\*6 Reversible logic gates

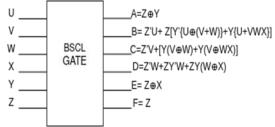

#### **BSCL GATE:**

Binary Coded Decimal Subtraction Correction gate is used to either find correction logic for BCD subtraction or to pass same data to the output depending on the control signal (Rashmi et al., 2011). The input vector is  $Iv=\{U,V,W,X,Y,Z\}$  and the output vector is  $Ov=\{Z \bigoplus Y\}$ ,

$Z'U+Z[Y'\{U\oplus(V+W)\}+Y\{U+VWX\}],$

$Z'V+[Y(V \oplus W)+Y(V \oplus WX)],Z'W+ZY'W+ZY(W)$

$\bigoplus X$ ),  $Z \bigoplus X$ , Z}. Here Z is the control signal, if Z is equal to 0,U,V,W,X,Y is passed as it is to the output. If Z is equal to 1 and if Y is equal to 0 then B, C, D and E is the nines complement of the input binary number U,V,W and X. If Y is equal to 1 then binary number 0001 is added to UVWX to get the valid corrected subtraction result.[19]

Table 1. Reversible logic gates Summarv

| SR.NO | GATE NAME           | ANTUMCOST | APPLICATION                           |

|-------|---------------------|-----------|---------------------------------------|

| 1     | CNOT/ Feynman Gate  | 1         | Duplication of output, inverter       |

| 2     | Toffoli Gate        | 5         | Universal logic gate                  |

| 3     | Fredkin Gate        | 5         | Swap operation                        |

| 4     | Peres Gate          | 4         | Subtractor                            |

| 5     | Double Feynman Gate | 2         | Parity preserving                     |

| 6     | BJN Gate            | 5         | Universal logic gate                  |

| 7     | RMUX1 Gate          | 4         | Multiplexer                           |

| 8     | TRG ate             | 4         | Subtractor                            |

| 9     | NEW Gate            | 4         | Adders                                |

| 10    | SAM Gate            | 4         | Flipflop Implementation               |

| 11    | NFT Gate            | 4         | Parity preserving                     |

| 13    | RC-1Gate            | 5         | Comparator                            |

| 14    | UPG Gate            | 4         | Universal logic gate                  |

| 15    | YAG Gate            | 4         | AND, OR, XNOR and EXOR Implementation |

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

| 16 | RMUX2 Gate        | 4           | Multiplexer                                  |

|----|-------------------|-------------|----------------------------------------------|

| 17 | HAS Gate          | 5           | Subtractor                                   |

| 18 | Double Peres Gate | 6           | Adders                                       |

| 19 | MRG Gate          | 6           | AND, OR, XNOR and EXOR Implementation        |

| 20 | SAYEM Gate        | 6           | Flipflop Implementation                      |

| 21 | TSG Gate          | 14          | Adders                                       |

| 22 | DKG Gate          | 17          | Adders                                       |

| 23 | SCL Gate          | Not Defined | Six correction to get actual BCD sum         |

| 24 | BVF Gate          | 2           | Extracting necessary outputs to meet fan-out |

| 25 | ALG Gate          | 11          | Adders                                       |

| 26 | PPHCG Gate        | 6           | Hamming error coding and detection.          |

| 27 | IG Gate           | 6           | AND, OR, XNOR and EXOR Implementation        |

| 28 | MKG Gate          | 13          | Universal logic gate                         |

| 29 | BME Gate          | 5           | Multiplier implementation                    |

| 30 | PTR Gate          | Not Defined | Adders                                       |

| 31 | PAOG Gate         | 6           | Universal logic gate                         |

Fig 1. Comparison of quantum cost of reversible logic gates

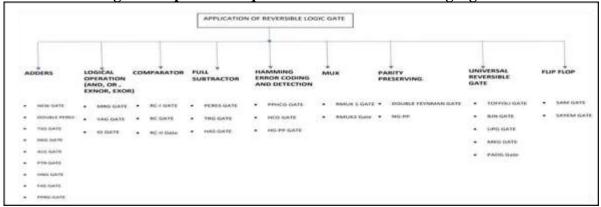

Fig 2. Application of reversible logic gate

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

## **VI Application of Reversible Logic Gates**

The advantages of reversible logic gates made it very popular for its usage in several applications as listed in figure 2. Reversible gates have been widely used for design of Binary and BCD adders, Multipliers, Sequential circuits, Arithmetic Logic Unit, Vedic Multipliers etc.

#### **CONCLUSION:**

In this literature survey, reversible logic gates and their applications from various research papers implemented til date are summarized. As reversible logic is attracting attention due to its advantages over CMOS technology, this overview of the reversible logic gates will help the designers implement complex digital circuits using reversible logic.

#### **REFERENCES:**

- [1] Ethan Mollick in, "Establishing Moore's Law", IEEE Annals of the History of Computing, 2006 IEEE.

- [2] R.Landauer in "Irreversibility and Heat Generation in the Computing Process", IBM JOURNAL, Research and Development, 5(3): pp. 183-191, 1961.

- [4] Charles H. Bennett in "Logical Reversibility of computation", IBM Journal of Research and Development, vol. 17, no. 6, pp. 525-532, 1973.

- [3] R. Keyes, R. Landauer in "Minimal energy dissipation in logic", IBM J. Res. Dev. 14(1970) 152–157.

- [4] Charles H. Bennett in "Logical Reversibility of computation", IBM Journal of Research and Development, vol. 17, no. 6, pp. 525-532, 1973.

- [5] Soham Bhattacharya, Anindya Sen in "A Review on Reversible Computing and it's applications on combinational circuits", et al., International Journal of Emerging Trends in Engineering Research, 9(6), June 2021, 806 814.

- [6] Himanshu Thapliyal, Nagarajan Ranganathan in "Design of Reversible Sequential Circuits Optimizing Quantum Cost, Delay, and Garbage Outputs", ACM Journal on Emerging Technologies in Computer Systems, Vol. 6, No. 4, Article 14, Pub. date: December 2010.

- [7] Aruna Rani, Poonam Kadam in "Adiabatic Split Level Charge Recovery Logic Circuit", International Journal of Computer Applications (0975 8887), vo 65– No.25, March 2013.

- [8] Papiya Biswas, Namit Gupta, Nilesh Patidar in "Basic Reversible Logic Gates and It's Qca Implementation", et al International Journal of Engineering Research and Applications, ISSN: 2248-9622, Vol. 4, Issue 6 (Version 5), June 2014, pp.12-16.

- [9] Vivek Singh, K. B. Ramesh in "Introduction to Reversible Logic Gates and its Operations", at International Journal for Research in Applied Science & Engineering Technology(IJRASET), ISSN: 2321-9653 Volume 10 Issue II Feb 2022.

- [10] Anamika Rockey Bhardwaj in "Reversible Logic Gates and its Performances", at 2nd International Conference on Inventive Systems and Control (ICISC),2018.

- [11] Anil Kumar Rajput, Santosh Chouhan, Manisha Pattanaik in "Low Power Boolean Logic Circuits using Reversible Logic Gates", International Conference on Advances in Computing, Communication and Control (ICAC3), IEEE 2019.

- [12] Snigdha Chowdhury Kolay, Subrata Chattopadhyay, Mandakinee Bandyopadhyay in "Design and Development of SS Reversible Logic Gate and it's Application as Adder & Subtractor", International Conference on Inventive Computation Technologies (ICICT), IEEE 2020.

- [13] H. M. Gaur, A. K. Singh, A. Mohan & D. K. Pradhan in "Computational Analysis and Comparison of Reversible Gates for Design and Test of Logic Circuits", International Journal of Electronics, Volume 106, 2019 Issue 11.

- [14] Md Saiful Islam, Zerina Begum in "Reversible Logic Synthesis of Fault Tolerant Carry Skip BCD Adder", Journal of Bangladesh Academy of Sciences, 32(2), 2008.

ISSN: 0970-2555

Volume: 52, Issue 8, No. 1, August: 2023

[15] Snigdha Singh, Abhinay Choudhary, Manoj Kumar Jai in "A Brief Overview Reversible Logic Gates and Reversible Circuits", International Journal Electronics Engineering (ISSN: 0973 - 7383) Volume 1 1 Issue 2 June - Dec 2019 pp. 8 6 - 1

04.

- [16] Matthew Morrison in "Design of a Reversible ALU Based on Novel Reversible Logic Structures", March 8, 2012.

- [17] Farah Sharmin, Rajib Kumar Mitra, Rashida Hasan, Anisur Rahman in "Low Cost Reversible Signed Comparator", International Journal of VLSI design & Communication Systems (VLSICS) Vol.4, No.5, October 2013.

- [18] Dr. Neelam Rup Prakash, Neha Pannu in "Generalized Approaches for ALU Design Using Reversible Gates" et al, (IJCSIT) International Journal of Computer Science and Information Technologies, Vol. 6 (6), 2015, 5292-5294.

- [19] Bahijja Yahaya Galadima, Garba Shehu Musa Galadanci, Abdulrazak Tijjani, M. Ibrahim in "A Review on Reversible logic gates", Bayero Journal of Pure and Applied Sciences 12(1):242-250, April 2020.

- [20] H R Bhagyalakshmi, M K Venkatesha in "Optimized design of BCD adder and Carry skip BCD adder using reversible logic gates", et al. International Journal on Computer Science and Engineering (IJCSE), ISSN: 0975-3397, Vol. 3 No. 4 Apr 2011.

- [21] Rajinder Tiwari, Deepika Bastawade, Preeta Sharan, Anil Kumar in "Performance Analysis of Reversible ALU in QCA"

- , Indian Journal of Science and Technology, Vol 10(29), DOI: 10.17485/ijst/2017/v10i29/117324, August 2017.

- [22] M. Arun, S. Saravanan in "Reversible Arithmetic Logic Gate (ALG) for Quantum Computation", International Journal of Intelligent Engineering and Systems Volume 6(3), September 2013.

- [23] Dhulipala Krishnaveni, Geetha Priya .M in "A Novel Design of Reversible Serial and Parallel Adder/ Subtractor", International Journal of Engineering Science and Technology (IJEST), ISSN: 0975-5462, Vol. 3 No. 3 March 2011.

- [24] D. Krishnaveni, M. Geetha Priya, K. Baskaran in "Design of an Efficient Reversible 8x8 Wallace Tree Multiplier", World Applied Sciences Journal 20(8): 1159-1165, ISSN 1818-4952, 2012.

- [25] Majid Haghparast, Keivan Navi in "A Novel Reversible Full Adder Circuit for Nanotechnology Based Systems", Journal of Applied Sciences, Volume: 7, Issue: 24, Page No.: 3995-4000, December 2007.

- [26] Ragani Khandelwal Sandeep Saini in "Parity Preserving Adder/Subtractor Using a Novel Reversible Gate", Fifth International Conference on Communication Systems and Network Technologies, 978-1-4799-1797-6/15, IEEE 2015

- [27] N Radha and M Maheswari in "An energy efficient multipliers using reversible gates", Journal of Physics: Conference Series, Volume 1706, First International Conference on Advances in Physical Sciences and Materials 13-14 August 2020.

- [28] Soham Bhattacharya, Sourav Goswami in "Truth Table Analysis of Logic Circuits using Reversible Gates", International Journal for Research in Applied Science & Engineering Technology (IJRASET) ISSN: 2321-9653 Volume 8 Issue II Feb (2020).

- [29] Mummadi Swathi, Dr. Bhawana Rudra in "Implementation of Reversible Logic Gates with Quantum Gates", 2021 IEEE Annual Computing and Communication Workshop and Conference.

- [30] P. Mohan Krishna, V. G. Santhi Swaroop, S. Harika, N. Sravya,

- V. Vani in "Implementation of Optimized Reversible Sequential and Combinational Circuits for VLSI Applications", International Journal

- of Engineering Research and Applications ISSN: 2248-9622, Vol. 4, Issue 4( Version 1), April 2014, pp.382-388.